SQ96A82L is the audio coding/decoding SoC IC with integrated USB/SD interfaces, featuring low cost, low power dissipation, high performance and high integration. With dual-core structure formed by low power dissipation MCU and high performance RISC, it is convenient for secondary development.

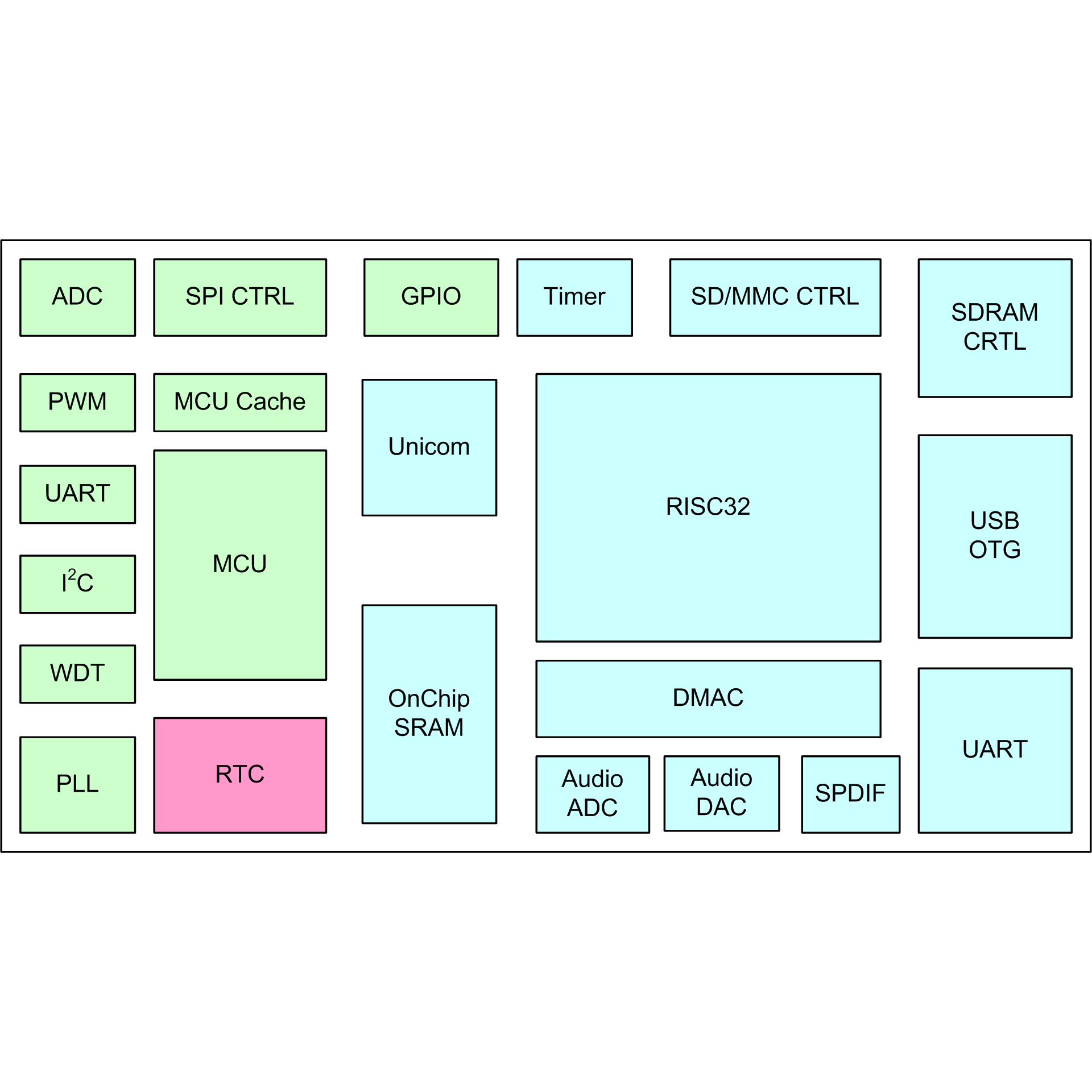

Architecture

Dual-core structure formed by low power dissipation 8-bit MCU and high performance 32-bit RISC.

Performance of MCU core is 4 times better than traditional 51, the instruction set is compatible with traditional MCS-51 instruction set.

CACHE+SPI structure, improves SPI flash access efficiency;

MCU can control read-write of SPI flash when the Cache is locked;

Internal RAM of MCU is 256 bytes, external RAM is 2K+512 bytes, the instruction space can be expanded to 8M byte through SPI flash.

High-performance 32-bit RISC core, 6-level pipelines.

Harvard cache architecture with separate 8KB Instruction and Data cache, single-cycle multiplication/accumulation operations, on-chip debugging (OCD) supported;

32-bit instruction and data space, with MMU function, operating system supported.

Clock & Power Manager

External 32.768KHz and 12MHz oscillators.

Built-in MCU PLL with 32.768KHz reference clock and System PLL12MHz reference clock, Audio PLL and USB PLL.

Clock frequency division control, MCU is able to work at 9-level frequencies in range of 32.768KHz ~ 24MHz, while RISC at 15-level frequencies in range of 30MHz ~ 162MHz.

Single 3.3V power supply, built-in DC-DC and LDO modules, provided to RISC and MCU cores.

RTC separately powered, with calendar function, 256-byte RAM which can save information when the main circuit is power failure.

Multi low-power operating modes supported, such as stop mode.

Memory Controller

SPI flash controller.

SPI Flash 1/2-wire modes;

Firmware in SPI flash able to be upgraded, can starting program from SPI flash;

MCU program is able to be run in SPI Flash, debugging code downloadable.

SDRAM controller.

High-efficiency SDRAM Interface, supports operation with 16-bit data;

Supporting SDRAM low-power modes, such as self-refresh, power down, etc.;

Packaged with SDRAM die of 1M*16-bit.

Peripherals

On-chip USB full/low speed controller, support host/device mode.

5 endpoints, three of which are INOUT type;

Integrated DMA , supports real-time transfer, interrupt transfer, bulk transfer, and control transfer;

Support USB wakeup and suspend;

Support USB audio application.

Integrated SD/MMC/SDIO controllers, supporting SD/MMC/SDIO protocol, general SPI supported.

Integrated high-speed UART controller.

Up to 4Mbps baud rate, with 64-byte buffer, DMA controlled data stream transmission.

Integrated two I2S control modules.

Supporting sampling rate up to 24-bit@192KHz.

DMA-controlled data stream transmission.

Integrated SPDIF output, sampling rate up to 24-bit@96KHz, DMA controlled data stream transmission.

Integrated one-channel 18-bit DAC, analog output LINEOUT_R and LINEOUT_L.

Integrated I2C host/slave control interfaces.

Integrated 4-channel PWM outputs.

Integrated 16-bit audio ADC.

2 channels, used for MIC,input, supporting audio superposition and simple reverberation processing;

Supporting saving the coded recorded data to SD or U disc.

Integrated 6-channel 10-bit ADC, can be used as keys, supporting MCU wake-up function.

Integrated programmable GPIO, four-grade drive current configurable (2mA/4mA/8mA/24mA), pull-up or open-drain configurable.

Other

Support ADPCM, MP3*, WMA*, LC-AAC*, OGG, FLAC*, APE* decode.

Support ADPCM and MP3* encode.

Able to embed EQ software.